M253

積層セラミックコンデンサの3D解析

チップ型の積層セラミックコンデンサは電子機器に多く使われており、小型・軽量化に大きく貢献しています。その内部は誘電体層と電極層が多層積層された構造となっています。今回、FIB-SEMトモグラフィにより、セラミックコンデンサの内部構造を3D解析しました。

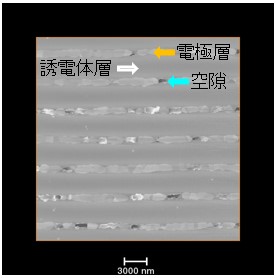

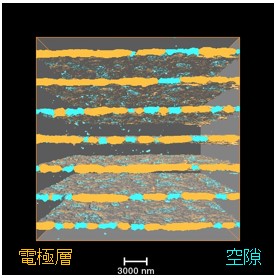

断面SEM像を図1に示します。誘電体層と電極層が交互に積層されています。また、電極層のところどころに空隙が認められます。FIB-SEMトモグラフィにより得られた三次元再構成像について、誘電体、電極、空隙をそれぞれセグメンテーション(領域分割)したデータを図2に示します。誘電体を白色透明、電極をオレンジ色、空隙を水色で表示しています。空隙は誘電体層中にも認められますが、多くは電極層に存在しています。

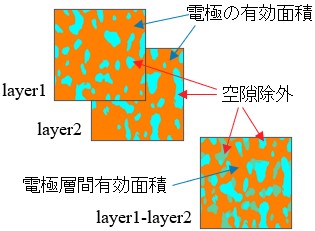

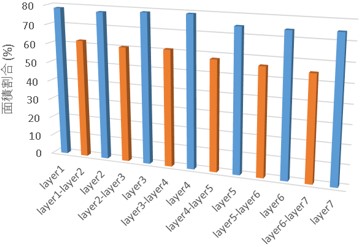

電極の面積はコンデンサの静電容量に影響すると考えられます。観察された7層の電極層について、空隙を除いた有効な面積(電極の有効面積)と、電極層間で互いに対向する面積(電極層間有効面積)を定義し (図3)、その割合を求めました(図4)。電極の有効面積は80%弱ですが、電極層間有効面積については、空隙の影響で60%程度になることが分かります。

以上のように、3D解析により、特性に影響し得る構造を数値的に評価することが可能です。